### **UWB Module**

### Product Overview

The MDM1000 module is based on Decawave's DW1000 Ultra Wideband (UWB) transceiver IC. It integrates antenna, all RF circuitry, power management and clock circuitry in one module. It can be used in 2-way ranging or TDOA location systems to locate assets to a precision of 10 cm and supports data rates of up to 6.8 Mbps

### Key Features

- IEEE 802.15.4-2011 UWB compliant

- Supports 4 RF bands from 3.5 GHz to 6.5 GHz

- Programmable transmitter output power

- Fully coherent receiver for maximum range and accuracy

- Designed to comply with FCC & ETSI UWB spectral masks

- Supply voltage 2.8 V to 3.6 V

- Low power consumption

- Data rates of 110 kbps,850 kbps, 6.8 Mbps

- Maximum packet length of 1023 bytes for high data throughput applications

- Integrated MAC support features

- Supports 2-way ranging and TDOA

- SPI interface to host processor

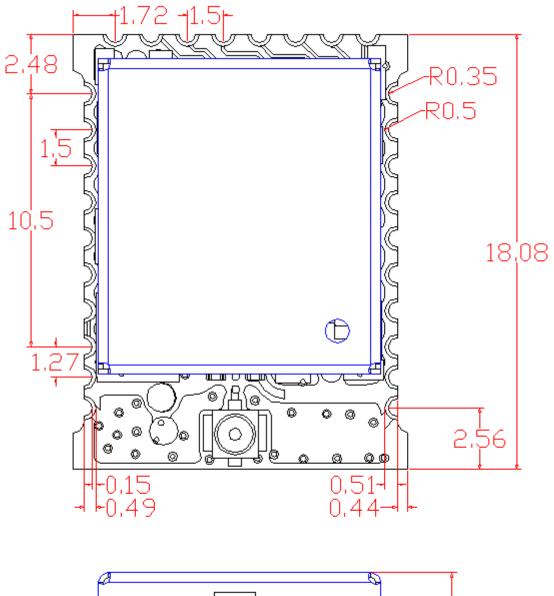

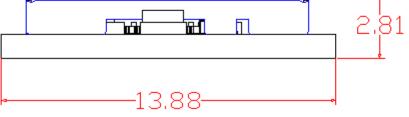

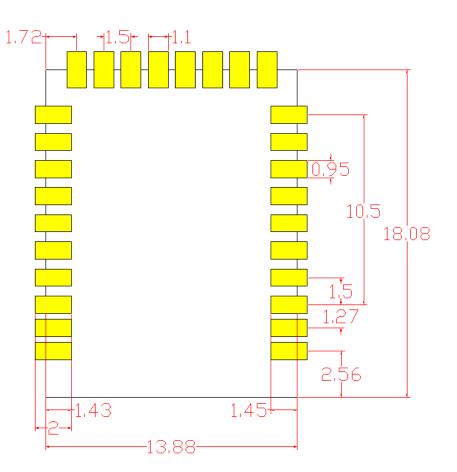

- 18.08 mm x 13.88 mm x 2.81 mm 28 pins

### Key Benefits

- Simplifies integration, no RF design required

- Very precise location of tagged objects delivers enterprise efficiency gains and cost reductions

Extended communications range minimises required infrastructure in RTLS

- High multipath fading immunity

- Supports very high tag densities in RTLS

- Low cost allows cost-effective implementation of solutions

- Low power consumption reduces the need to replace batteries and lowers system lifetime costs

### Applications

- Precision real time location systems (RTLS) using two-way ranging or TDOA schemes in a variety of markets.

- Location aware wireless sensor networks (WSNs)

# **1 OVERVIEW**

The MDM1000 module is an IEEE 802.15.4-2011 UWB implementation. RF components, Decawave DW1000 UWB transceiver, and other components reside on-module. MDM1000 enables cost effective and reduced complexity integration of UWB communications and ranging features, greatly accelerating design implementation.

### 1.1 MDM1000 Functional Description

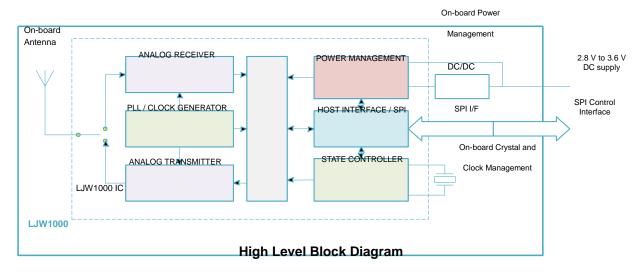

The DW1000 on board the MDM1000 is a fully integrated low-power, single chip CMOS RF transceiver IC compliant with the IEEE 802.15.4-2011 [1] UWB standard. The MDM1000 module requires no RF design as the antenna and associated analog and RF components are on the module.

The module contains an on-board 38.4 MHz reference crystal. The crystal has been trimmed in production to reduce the initial frequency error to approximately 2 ppm, using the DW1000 IC's internal on-chip crystal trimming circuit, see section 2.1.1.

Always-On (AON) memory can be used to retain MDM1000 configuration data during the lowest power operational states when the on-chip voltage regulators are disabled. This data is uploaded and downloaded automatically. Use of MDM1000 AON memory is configurable.

The on-chip voltage and temperature monitors allow the host to read the voltage on the VDDAON pin and the internal die temperature information from the DW1000.

See the DW1000 Datasheet [2] for more detailed information on device functionality, electrical specifications and typical performance.

# 3.3 V Supplies (VDDAON / VDD / VDD) EXTON RSTn Text\_on Tdia on

OFF

# 1.2 MDM1000 Power Up

#### Figure 1. MDM1000 Power-up Sequence

INIT

POWER UP

When power is applied to the MDM1000, RSTn is driven low by internal circuitry as part of its power up sequence. See Figure 1 above. RSTn remains low until the on-module crystal oscillator has powered up and its output is suitable for use by the rest of the device, at which time RSTn is deasserted high.

#### Table 1: DW1000 Power-up Timings

STATE

| Parameter | Description                                                                    | Nominal Value | Units |

|-----------|--------------------------------------------------------------------------------|---------------|-------|

| VON       | Voltage threshold to enable power up                                           | 2.0           | V     |

| TEXT_ON   | Time at which EXTON goes high before RSTn is released                          | 3             | ms    |

| TDIG_ON   | RSTn held low by internal reset circuit / driven low by external reset circuit | 3             | ms    |

RSTn may be used as an output to reset external circuitry as part of system bring-up as power is applied.

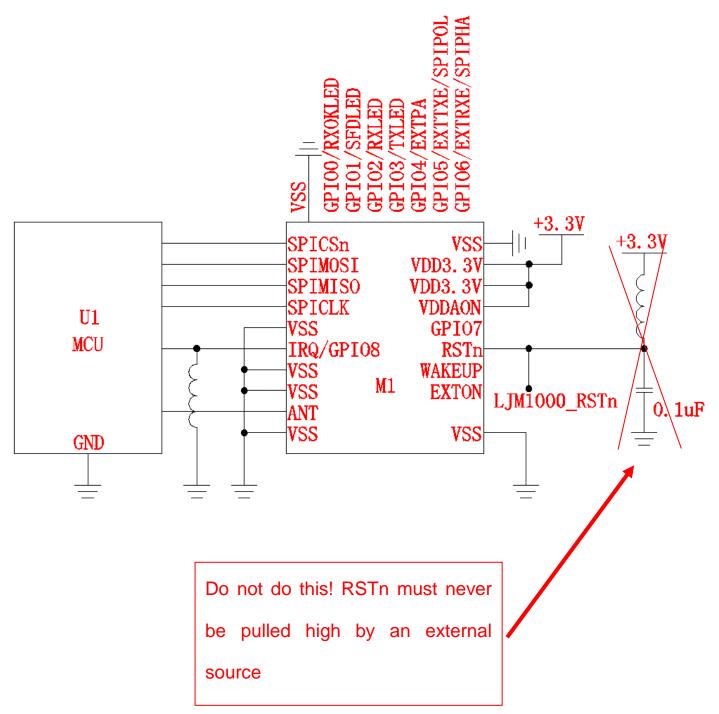

An external circuit can reset the MDM1000 by asserting RSTn for a minimum of 10 ns. RSTn is an asynchronous input. DW1000 initialization will proceed when the pin is released to high impedance. **RSTn should never be driven high by an external source.** Please see DW1000 Datasheet [2] for more details of DW1000 power up.

### 1.3 SPI Host Interface

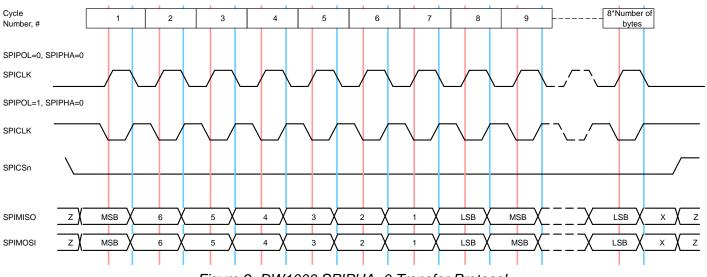

The DW1000 host communications interface is a slave-only SPI. Both clock polarities (SPIPOL=0/1) and phases (SPIPHA=0/1) are supported. The data transfer protocol supports single and multiple byte read/writes accesses. All bytes are transferred MSB first and LSB last. A transfer is initiated by asserting SPICSn low and terminated when SPICSn is deasserted high.

See the DW1000 Datasheet [2] for full details of the SPI interface operation and mode configuration for clock phase and polarity.

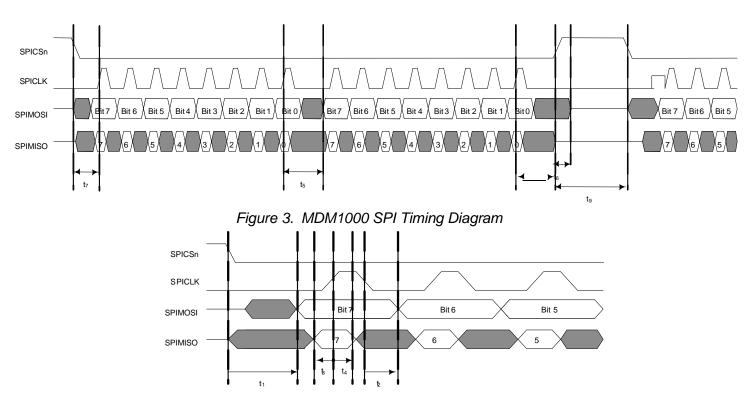

# 1.3.1 SPI Signal Timing

Figure 4. MDM1000 SPI Detailed Timing Diagram

| Parameter      | Min | Тур | Max | Unit | Description                                                    |

|----------------|-----|-----|-----|------|----------------------------------------------------------------|

| SPICLK Period  | 50  |     |     | ns   | The maximum SPI frequency is 20 MHz when the CLKPLL is locked, |

| OF ICENT EIIOG | 50  |     |     |      | otherwise the maximum SPI frequency is 3 MHz.                  |

| t1             |     |     | 38  | ns   | SPICSn select asserted low to valid slave output data          |

| t2             | 12  |     |     | ns   | SPICLK low to valid slave output data                          |

| t3             | 10  |     |     | ns   | Master data setup time                                         |

| t4             | 10  |     |     | ns   | Master data hold time                                          |

#### Table 2: MDM1000 SPI Timing Parameters

| Parameter | Min | Тур | Max | Unit                                            | Description                                           |  |  |  |

|-----------|-----|-----|-----|-------------------------------------------------|-------------------------------------------------------|--|--|--|

| t5        | 32  |     |     | ns                                              | LSB last byte to MSB next byte                        |  |  |  |

| t6        |     |     | 10  | ns SPICSn de-asserted high to SPIMISO tri-state |                                                       |  |  |  |

| t7        | 16  |     |     | ns                                              | Start time; time from select asserted to first SPICLK |  |  |  |

| t8        | 40  |     |     | ns                                              | ns Idle time between consecutive accesses             |  |  |  |

| t9        | 40  |     |     | ns                                              | ns Last SPICLK to SPICSn de-asserted                  |  |  |  |

# 1.4 General Purpose Input Output (GPIO)

The MDM1000 provides 8 configurable pins.

On reset, all GPIO pins default to input. GPIO inputs, when appropriately configured, are capable of generating interrupts to the host processor via the IRQ signal.

GPIO0, 1, 2, & 3, as one of their optional functions, can drive LEDs to indicate the status of various chip operations. Any GPIO line being used to drive an LED in this way should be connected as shown. GPIO5 & 6 are used to configure the operating mode of the SPI as described in the DW1000 Datasheet [2].

See DW1000 Datasheet [2] and DW1000 User Manual [3] provide full details of the configuration and use of the GPIO lines.

#### 1.5 Always-On (AON) Memory

Configuration retention in lowest power states is enabled in MDM1000 by provision of an Always-On (AON) memory array with a separate power supply, VDDAON. The MDM1000 may be configured to upload its configuration to AON before entering a low-power state and to download the configuration when waking up from the low –power state.

#### 1.6 One-Time Programmable (OTP) Memory

The MDM1000 contains a 56x32 -bit user programmable OTP memory on the DW1000 device that is used to store per chip calibration information.

#### **1.7 Interrupts and Device Status**

MDM1000 has a number of interrupt events that can be configured to drive the IRQ output pin. The default IRQ pin polarity is active high. A number of status registers are provided in the system to monitor and report data of interest. See DW1000 User Manual [3] for a full description of system interrupts and their configuration and of status registers.

#### 1.8 MAC

A number of MAC features are implemented including CRC generation, CRC checking and receive frame filtering. See the DW1000 Datasheet [2] and DW1000 User Manual [3] for full details.

# 2 MDM1000 CALIBRATION

Depending on the end-use application s and the system design, MDM1000 settings may need to be tuned. To help with this tuning a number of built in functions such as continuous wave TX and continuous packet transmission can be enabled. See the DW1000 User Manual [3] for further details.

# 2.1 Crystal Oscillator Trim

MDM1000 modules are calibrated at production to minimise initial frequency error to reduce carrier frequency offset between modules and thus improve receiver sensitivity. The calibration carried out at module production will trim the initial frequency offset to less than 2 ppm, typically.

### 2.3 Transmitter Calibration

In order to maximise range, MDM1000 transmit power spectral density (PSD) should be set to the maximum allowable for the geographic region in which it will be used. For most regions this is -41.3 dBm/MHz.

As the module contains an integrated antenna, the transmit power can only be measured over the air. The Effective Isotropic Radiated Power (EIRP) must be measured and the power level adjusted to ensure compliance with applicable regulations.

The MDM1000 provides the facility to adjust the transmit power in coarse and fine steps; 3 dB and 0.5 dB nominally. It also provides the ability to adjust the spectral bandwidth. These adjustments can be used to maximise transmit power whilst meeting regulatory spectral mask.

If required, transmit calibration should be carried out on a per MDM1000 module basis, see DW1000 User Manual [3] for full details.<sup>1</sup>

### 2.4 Antenna Delay Calibration

In order to measure range accurately, precise calculation of timestamps is required. To do this the antenna delay must be known. The MDM1000 allows this delay to be calibrated and provides the facility to compensate for delays introduced by PCB, external components, antenna and internal MDM1000 delays.

To calibrate the antenna delay, range is measured at a known distance using two MDM1000 systems. Antenna delay is adjusted until the known distance and reported range agree. The antenna delay can be stored in OTP memory.

Antenna delay calibration must be carried out as a once off measurement for each MDM1000 design implementation. If required, for greater accuracy, antenna delay calibration should be carried out on a per MDM1000 module basis, see DW1000 User Manual [3] for full details.

# **3 MDM1000 PIN CONNECTIONS**

# 3.1 Pin Numbering

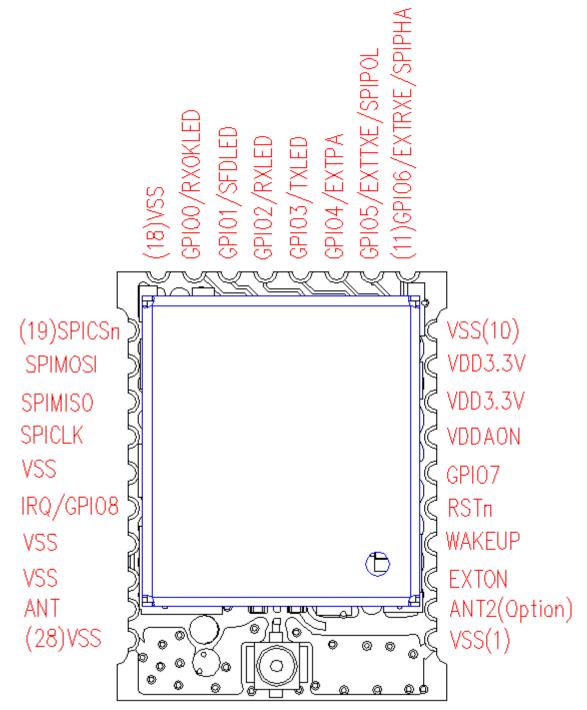

MDM1000 module pin assignments are as follows (viewed from top):

Figure 5. MDM1000 Pin Diagram

# 3.2 Pin Descriptions

.

Table 3: MDM1000 Pin functions

| SIGNAL NAME         | PIN                     | I/O (Default) | DESCRIPTION                                                              |  |  |  |

|---------------------|-------------------------|---------------|--------------------------------------------------------------------------|--|--|--|

| VSS                 | 1,10,18,23,<br>25,26,28 | G             | Common ground.                                                           |  |  |  |

| ANT                 | 2,27                    | 0             | Module Antenna terminal, Default terminal                                |  |  |  |

|                     |                         |               | External device enable. Asserted during wake up process and held         |  |  |  |

|                     |                         |               | active until device enters sleep mode. Can be used to control external   |  |  |  |

| EXTON               | 3                       | DO (O-L)      | DC-DC converters or other circuits that are not required when the device |  |  |  |

|                     |                         |               | is in sleep mode so as to minimize power consumption. Refer to           |  |  |  |

|                     |                         |               | DW1000 Datasheet for more details [2].                                   |  |  |  |

|                     |                         |               | When asserted into its active high state, the WAKEUP pin brings the      |  |  |  |

| WAKEUP              | 4                       | DIO           | DW1000 out of SLEEP or DEEPSLEEP states into operational mode.           |  |  |  |

|                     |                         |               | If unused, this pin can be tied to ground.                               |  |  |  |

|                     |                         |               | Reset pin. Active Low Output.                                            |  |  |  |

| RSTn                | 5                       | DIO (O-H)     | May be pulled low by external open drain driver to reset the DW1000.     |  |  |  |

|                     |                         |               | Refer to DW1000 Datasheet for more details [2].                          |  |  |  |

|                     |                         |               | Defaults to operate as a SYNC input – refer [2].                         |  |  |  |

| GPIO7               | 6                       | DIO (I)       | THIS FUNCTIONALITY IS NOT APPLICABLE TO THE MDM1000.                     |  |  |  |

|                     |                         |               | This pin may be reconfigured as a general purpose I/O pin, GPIO7         |  |  |  |

|                     |                         |               | under software control.                                                  |  |  |  |

| VDDAON              | 7                       | Р             | External supply for the Always-On (AON) portion of the chip.             |  |  |  |

|                     |                         |               | 3.3 V supply pins. Note that for programming the OTP in the MDM1000      |  |  |  |

| VDD3.3V             | 8,9                     | Р             | module this voltage may be increased to a nominal value of 3.8 V for     |  |  |  |

|                     |                         |               | short periods.                                                           |  |  |  |

|                     |                         |               | General purpose I/O pin.                                                 |  |  |  |

|                     |                         |               | On power-up it acts as the SPIPHA (SPI phase selection) pin for          |  |  |  |

| GPIO6/EXTRXE/SPIPHA | 11                      | DIO (I)       | configuring the SPI mode of operation. Refer to Section 5.2.2 and the    |  |  |  |

|                     |                         |               | DW1000 Datasheet for more details [2].                                   |  |  |  |

|                     |                         |               | After power-up, the pin will default to a General Purpose I/O pin.       |  |  |  |

|                     |                         |               | General purpose I/O pin.                                                 |  |  |  |

|                     | 10                      |               | On power-up it acts as the SPIPOL (SPI polarity selection) pin for       |  |  |  |

| GPIO5/EXTTXE/SPIPOL | 12                      | DIO (I)       | configuring the SPI operation mode. Refer to Section 5.2.2 and the       |  |  |  |

|                     |                         |               | DW1000 Datasheet for more details [2].                                   |  |  |  |

|                     | 40                      |               | After power-up, the pin will default to a General Purpose I/O pin.       |  |  |  |

| GPIO4/EXTPA         | 13                      | DIO (I)       | General purpose I/O pin.                                                 |  |  |  |

|                     |                         |               | General purpose I/O pin.                                                 |  |  |  |

| GPIO3/TXLED         | 14                      | DIO (I)       | It may be configured for use as a TXLED driving pin that can be used to  |  |  |  |

|                     |                         |               | light a LED following a transmission. Refer to the DW1000 User Manual    |  |  |  |

|                     |                         |               | [2] for details of LED use.                                              |  |  |  |

|                     |                         |               | General purpose I/O pin.                                                 |  |  |  |

| GPIO2/RXLED         | 15                      | DIO (I)       | It may be configured for use as a RXLED driving pin that can be used to  |  |  |  |

|                     |                         |               | light a LED during receive mode. Refer to the DW1000 User Manual [2]     |  |  |  |

|                     |                         |               | for details of LED use.                                                  |  |  |  |

|               |    |           | General purpose I/O pin.                                                  |  |  |  |  |

|---------------|----|-----------|---------------------------------------------------------------------------|--|--|--|--|

| GPIO1/SFDLED  | 16 | DIO (I)   | It may be configured for use as a SFDLED driving pin that can be used     |  |  |  |  |

|               | 10 |           | to light a LED when SFD (Start Frame Delimiter) is found by the           |  |  |  |  |

|               |    |           | receiver. Refer to the DW1000 User Manual [2] for details of LED use.     |  |  |  |  |

|               |    |           | General purpose I/O pin.                                                  |  |  |  |  |

|               | 47 |           | It may be configured for use as a RXOKLED driving pin that can be used    |  |  |  |  |

| GPIO0/RXOKLED | 17 | DIO (I)   | to light a LED on reception of a good frame. Refer to the DW1000 User     |  |  |  |  |

|               |    |           | Manual [2] for details of LED use.                                        |  |  |  |  |

|               |    |           | SPI chip select. This is an active low enable input. The high-to-low      |  |  |  |  |

|               | 19 | DI        | transition on SPICSn signals the start of a new SPI transaction.          |  |  |  |  |

| SPICSn        |    |           | SPICSn can also act as a wake-up signal to bring DW1000 out of either     |  |  |  |  |

|               |    |           | SLEEP or DEEPSLEEP states Refer to DW1000 Datasheet for more              |  |  |  |  |

|               |    |           | details [2].                                                              |  |  |  |  |

| SPIMOSI       | 20 | DI        | SPI data input. Refer to DW1000 Datasheet for more details [2].           |  |  |  |  |

| SPIMISO       | 21 | DO (O–L)  | SPI data output. Refer to DW1000 Datasheet for more details [2].          |  |  |  |  |

| SPICLK        | 22 | DI        | SPI clock                                                                 |  |  |  |  |

|               |    |           | Interrupt Request output from the MDM1000 to the host processor. By       |  |  |  |  |

|               |    |           | default IRQ is an active-high output but may be configured to be active   |  |  |  |  |

|               |    |           | low if required. For correct operation in SLEEP and DEEPSLEEP modes       |  |  |  |  |

|               |    |           | it should be configured for active high operation. This pin will float in |  |  |  |  |

| IRQ/GPIO8     | 24 | DIO (O-L) | SLEEP and DEEPSLEEP states and may cause spurious interrupts              |  |  |  |  |

|               |    |           | unless pulled low.                                                        |  |  |  |  |

|               |    |           | When the IRQ functionality is not being used the pin may be               |  |  |  |  |

|               |    |           | reconfigured as a general purpose I/O line, GPIO8.                        |  |  |  |  |

|               |    |           |                                                                           |  |  |  |  |

# Table 4: Explanation of Abbreviations

| ABBREVIATION            | EXPLANATION                                  |  |  |  |  |  |

|-------------------------|----------------------------------------------|--|--|--|--|--|

| I                       | Input                                        |  |  |  |  |  |

| IO                      | Input / Output                               |  |  |  |  |  |

| 0                       | Output                                       |  |  |  |  |  |

| G                       | Ground                                       |  |  |  |  |  |

| Р                       | Power Supply                                 |  |  |  |  |  |

| PD                      | Power Decoupling                             |  |  |  |  |  |

| O-L                     | Defaults to output, low level after reset    |  |  |  |  |  |

| O-H                     | Defaults to output, high level after reset   |  |  |  |  |  |

| I                       | Defaults to input.                           |  |  |  |  |  |

| ote: Any signal with th | e suffix 'n' indicates an active low signal. |  |  |  |  |  |

I.

# **4 ELECTRICAL SPECIFICATIONS**

# 4.1 Nominal Operating Conditions

Table 5: MDM1000 Operating Conditions

| Parameter                                                   | Min. | Тур. | Max. | Units | Condition/Note                                                                                                                     |

|-------------------------------------------------------------|------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Operating temperature                                       | -40  |      | +85  | °C    |                                                                                                                                    |

| Supply voltage VDDAON, VDD3V3                               | 2.8  | 3.3  | 3.6  | V     | Normal operation                                                                                                                   |

| Supply voltage VDD3V3 for programming OTP                   | 3.7  | 3.8  | 3.9  | V     | Note that for programming the OTP<br>in the MDM1000 the VDD3V3<br>voltage must be increased to 3.8 V<br>nominal for short periods. |

| Voltage on GPIO07, WAKEUP, RSTn, SPICSn,<br>SPIMOSI, SPICLK |      |      | 3.6  | V     | Note that 3.6 V is the max voltage that may be applied to these pins                                                               |

Note: Unit operation is guaranteed by design when operating within these ranges

### 4.2 DC Characteristics

Tamb = 25 °C, all supplies centred on typical values

Table 6: MDM1000 DC Characteristics

| Parameter                           | Min.    | Тур. | Max.    | Units | Condition/Note                         |

|-------------------------------------|---------|------|---------|-------|----------------------------------------|

| Supply current DEEP SLEEP mode      |         | 200  |         | nA    |                                        |

| Supply current SLEEP mode           |         | 550  |         | nA    | Total current drawn from all           |

| Supply current IDLE mode            |         | 13.4 |         | mA    | supplies.                              |

| Supply current INIT mode            |         | 3.5  |         | mA    |                                        |

| TX :3.3 V supplies<br>(VDDAON, VDD) |         |      | 140     | mA    | Channel 5:TX Power:<br>9.3 dBm/500 MHz |

| RX :3.3 V supplies<br>(VDDAON, VDD) |         |      | 160     | mA    | Channel 5                              |

| Digital input voltage high          | 0.7*VDD |      |         | V     |                                        |

| Digital input voltage low           |         |      | 0.3*VDD | V     |                                        |

| Digital output voltage high         | 0.7*VDD |      |         | V     | Assumes 500 $\Omega$ load              |

| Digital output voltage low          |         |      | 0.3*VDD | V     | Assumes 500 $\Omega$ load              |

| Digital Output Drive Current        |         |      |         |       |                                        |

| GPIOx, IRQ                          | 4       | 6    |         | m (   |                                        |

| SPIMISO                             | 8       | 10   |         | mA    |                                        |

| EXTON                               | 3       | 4    |         |       |                                        |

### **4.3 Receiver AC Characteristics**

Tamb = 25 °C, all supplies centred on nominal values

Table 7: MDM1000 Receiver AC Characteristics

| Parameter                  | Min. | Тур. | Max. | Units | Condition/Note             |

|----------------------------|------|------|------|-------|----------------------------|

| Frequency range            | 3244 |      | 6999 | MHz   |                            |

| Channel bandwidth          |      | 500  |      | MHz   | Channel 1,2,3 and 5        |

| In-band blocking level     |      | 30   |      | dBc   | Continuous wave interferer |

| Out-of-band blocking level |      | 55   |      | dBc   | Continuous wave interferer |

### 4.4 Receiver Sensitivity Characteristics

Tamb = 25 °C, all supplies centred on typical values. 20 byte payload. These sensitivity figures assume an antenna gain of 0 dBi and should be modified by the antenna characteristics quoted in Table 12 depending on the orientation of the MDM1000.

| Packet<br>Error<br>Rate | Data<br>Rate | Receiver<br>Sensitivity | Units                 | Condition/Note       |                                        |                                                                                                             |  |  |  |  |

|-------------------------|--------------|-------------------------|-----------------------|----------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                         | 110 kbps     | -102                    | dBm/500<br>MHz        | Preamble<br>2048     |                                        |                                                                                                             |  |  |  |  |

| 1%                      | 850 kbps     | -101                    | dBm/500               | Preamble             |                                        | All measurements performed<br>on Channel 5, PRF 16 MHz<br>Channel 2 is approximately 1<br>dB less sensitive |  |  |  |  |

|                         | 6.8 Mbps     | -93                     | MHz<br>dBm/500<br>MHz | 1024<br>Preamble 256 | Carrier<br>frequency offset<br>±10 ppm |                                                                                                             |  |  |  |  |

|                         | 110 kbps     | -106                    | dBm/500<br>MHz        | Preamble<br>2048     |                                        |                                                                                                             |  |  |  |  |

| 10%                     | 850 kbps     | -102                    | dBm/500<br>MHz        | Preamble<br>1024     |                                        |                                                                                                             |  |  |  |  |

|                         | 6.8 Mbps     | -94                     | dBm/500<br>MHz        | Preamble 256         |                                        |                                                                                                             |  |  |  |  |

### 4.5 Reference Clock AC Characteristics

Tamb = 25 °C, all supplies centred on typical values

#### 4.5.1 Reference Frequency

Table 9: MDM1000 Reference Clock AC Characteristics

| Parameter                                             | Min. | Тур. | Max. | Units      | Condition/Note                                            |

|-------------------------------------------------------|------|------|------|------------|-----------------------------------------------------------|

| On-board crystal oscillator reference frequency       |      | 38.4 |      | MHz        |                                                           |

| On-board crystal trimming range                       |      | ±25  |      | ppm        | Internally trimmed to +/- 2 ppm under typical conditions. |

| On-board crystal frequency stability with temperature |      |      | ±30* | ppm<br>ppm | -40°C to +85°                                             |

| On-board crystal aging                                |      |      | ±3   | ppm/3year  | @25°C ±2°C                                                |

| Low Power RC Oscillator                               | 5    | 12   | 15   | kHz        |                                                           |

**MDM1000**

\*By using the temperature monitoring capability of the DW1000 chip on the MDM1000 module it is possible to dynamically trim the crystal during run time to maintain the +/- 2ppm specification over the full temperature range of operation.

# 4.6 Transmitter AC Characteristics

Tamb = 25 °C, all supplies centred on typical values

#### Table 10: MDM1000 Transmitter AC Characteristics

| Parameter                                    | Min. | Тур.         | Max. | Units   | Condition/Note           |

|----------------------------------------------|------|--------------|------|---------|--------------------------|

| Frequency range                              | 3244 |              | 6999 | MHz     |                          |

| Channel Bandwidths                           |      | 500          |      | MHz     | Channel 1, 2, 3 and 5    |

| Output power spectral density (programmable) |      | -39          | -35  | dBm/MHz | See DW1000 Datasheet [2] |

| Power level range                            |      | 37           |      | dB      |                          |

| Coarse Power level step                      |      | 3            |      | dB      |                          |

| Fine Power level step                        |      | 0.5          |      | dB      |                          |

| Output power variation with temperature      |      | 0.05         |      | dB/OC   |                          |

| Output power variation with voltage          |      | 2.73<br>3.34 |      | dB/V    | Channel 2<br>Channel 5   |

# 4.7 Temperature and Voltage Monitor Characteristics

Table 11: MDM1000 Temperature and Voltage Monitor Characteristics

| Parameter                     | Min. | Тур. | Max. | Units | Condition/Note |

|-------------------------------|------|------|------|-------|----------------|

| Voltage Monitor Range         | 2.4  |      | 3.75 | V     |                |

| Voltage Monitor Precision     |      | 20   |      | mV    |                |

| Voltage Monitor Accuracy      |      | 140  |      | mV    |                |

| Temperature Monitor Range     | -40  |      | +100 | °C    |                |

| Temperature Monitor Precision |      | 0.9  |      | °C    |                |

### 4.8 Absolute Maximum Ratings

Table 12: MDM1000 Absolute Maximum Ratings

| Parameter                           | Min. | Max. | Units |

|-------------------------------------|------|------|-------|

| Voltage                             | -0.3 | 4.0  | V     |

| VDD3V3 / VDDAON                     | 0.0  | 1.0  | ,     |

|                                     |      |      |       |

| Receiver Power                      |      | 0    | dBm   |

|                                     |      |      |       |

| Temperature - Storage temperature   | -40  | +85  | °C    |

| Temperature – Operating temperature | -40  | +85  | °C    |

|                                     |      |      |       |

| ESD (Human Body Model)              |      | 2000 | V     |

Stresses beyond those listed in this table may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions beyond those indicated in the operating conditions of the specification is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

# **5** Application Information

# 6 Module Package OutlineDrawing

Unit: mm

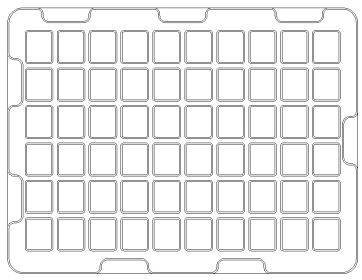

# 7 Recommended PCB Land Pattern

Unit: mm

# 8 Tray packaging

Figure 6. Package Outline Drawing

Note:

tray packaging, 60pcs/tray.

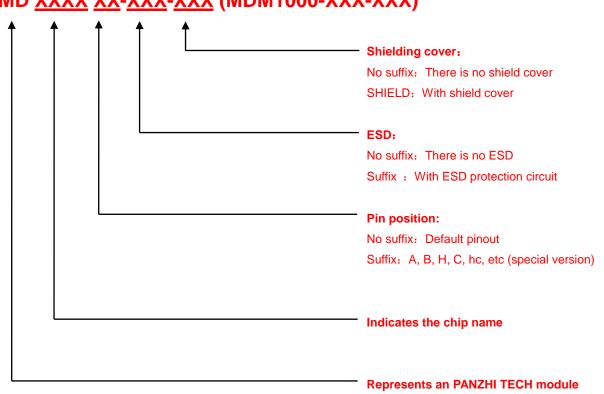

# 9 Ordering Information:

# MD XXXX XX-XXX-XXX (MDM1000-XXX-XXX)

# **10 Module Revisions**

Table 13. Revision History

| Revisions | Date        | Updated History         |  |  |

|-----------|-------------|-------------------------|--|--|

| Rev1.0    | August 2018 | The first final release |  |  |

|           |             |                         |  |  |

# 11 Contact us:

DONGGUAN PANZHI TECH CO., LTD

Address:Room 5162, Building 3, No.8 Jingcheng Second Road, Huangjiang Town, Dongguan City, Guangdong Province, China

E-mail: sales@panzhitech.com

Http:// www.panzhitech.com

All Rights Reserved. PANZHI TECH reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. The information contained within is believed to be accurate and reliable. However, PANZHI TECH does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein.